SPICE3-hacking primer

Contents

- 1 Meh?

- 2 Real docs

- 3 Examples

- 3.1 Piece-wise linear: voltage-source with V/t-curve consisting of line segments

- 3.2 AC (frequency-) analysis of a simple low-pass filter

- 3.3 Initial conditions: giving a component an initial value

- 3.4 DC-sweep: ramp a (voltage-)source from start- to end-value

- 3.5 Current-measurement using a dummy voltage-source (0V)

- 3.6 Pulsed source using nonzero rise- and fall-times

- 3.7 Physical pushbutton switch using helper voltage-source

- 3.8 Voltage-controlled voltage-source as sad excuse for opamp-model

Meh?

I heard a lot about SPICE, and never used it outside of one of its many fuzzy packages, e.g. PSpice. Googling by accident showed that SPICE-models representing simple circuits can be extremely short, so let's try.

If you spot an obvious mistake, please tell or change this page.

My goal here was clearly to simulate small and isolated parts of circuits using mainly passive components; a simple setup can be hacked together and simulated, well, within tens of seconds, really.

A lot of funny plots are about to greet your eyes. SPICE can do a lot more than all this.

I use the ngspice incarnation on a NetBSD system, plotting directly to my monitor.

Real docs

I don't like the original SPICE3 docs; I guess everything is explained, but it feels incoherent and IMHO it could have been twice as long without being too long.

TBD - ori docs in var fgormats - wikipedia - spice models from downstairs pc - spice docs from mail TBD

Examples

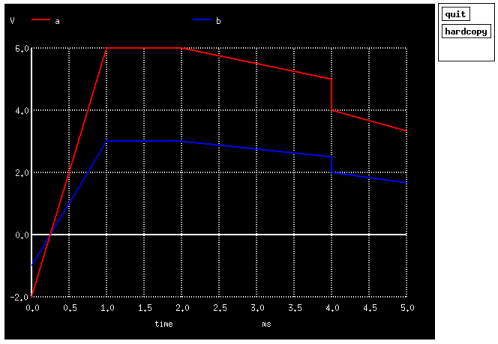

Piece-wise linear: voltage-source with V/t-curve consisting of line segments

this text should be below table

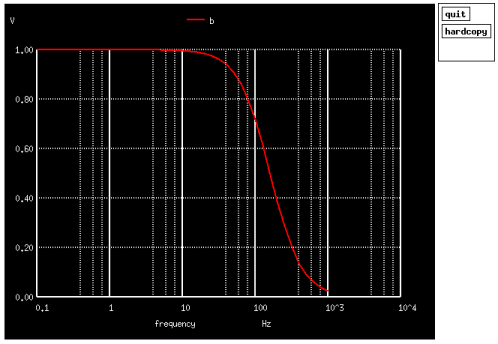

AC (frequency-) analysis of a simple low-pass filter

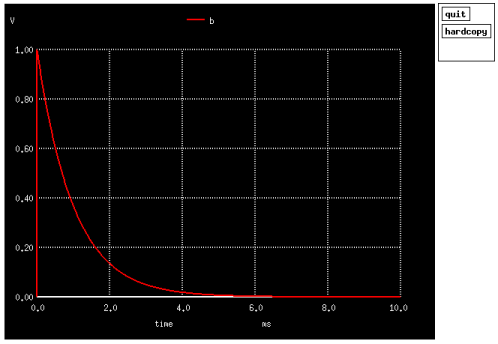

Initial conditions: giving a component an initial value

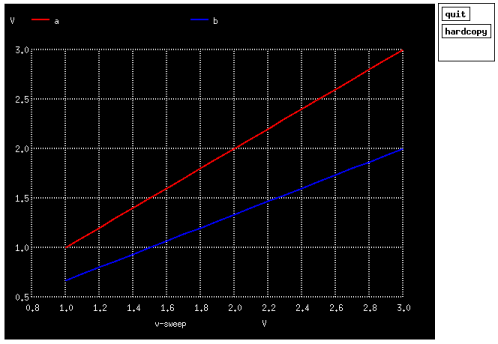

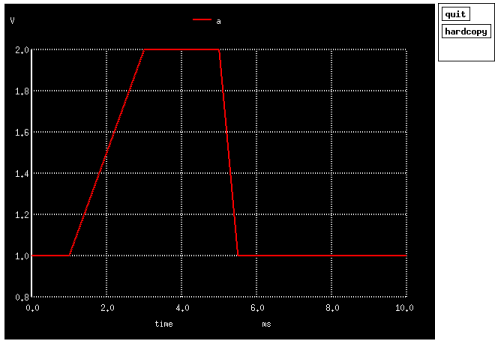

DC-sweep: ramp a (voltage-)source from start- to end-value

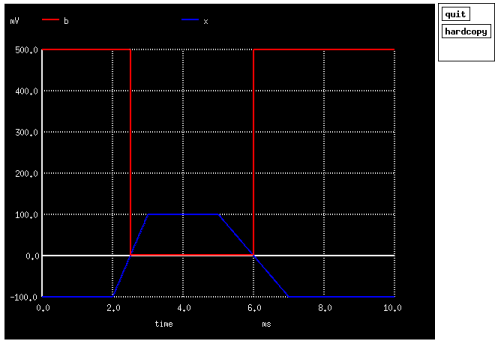

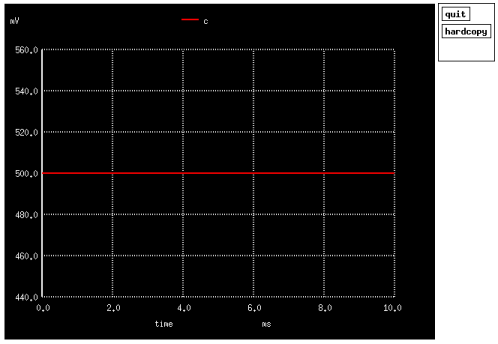

Current-measurement using a dummy voltage-source (0V)

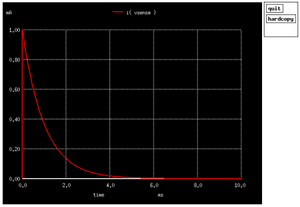

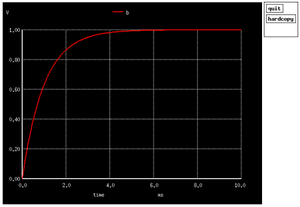

transient analysis: current-measurement using 0V voltage source *** Dummy (0 V) voltage-source 'vsense' between resistor and cap v a 0 dc 1 r a b 1k vsense b c dc 0 c c 0 1u *** Show current through dummy voltage source, and (effectively) cap voltage * * CAVEAT: 'uic' _must_ be added, else cap behaves as open circuit .control tran 10u 10m uic plot i( vsense ) plot b .endc .end |