Difference between revisions of "1-wire bitbanging"

(subsections) |

|||

| Line 1: | Line 1: | ||

| − | = One wire overview = | + | == One wire overview == |

| − | == TL;DR == | + | === TL;DR === |

This is a short overview about 1-wire bus, so the implementation of bitbanging below will make sense. | This is a short overview about 1-wire bus, so the implementation of bitbanging below will make sense. | ||

| Line 13: | Line 13: | ||

Use a pull-up of 1-5k. | Use a pull-up of 1-5k. | ||

| − | == Link layer == | + | === Link layer === |

I will only mention regular speed, overdrive is similar, only timings are different. | I will only mention regular speed, overdrive is similar, only timings are different. | ||

Line is driven high by a pull-up, so master and slave basically only signal zeroes. | Line is driven high by a pull-up, so master and slave basically only signal zeroes. | ||

| − | === Reset pulse === | + | ==== Reset pulse ==== |

Reset puts the device into predefined state. It's just a 480us+ low pulse followed by 480us+ high in which time devices mark their presence. | Reset puts the device into predefined state. It's just a 480us+ low pulse followed by 480us+ high in which time devices mark their presence. | ||

| − | === Write 0 === | + | ==== Write 0 ==== |

This is a 60-120us long low pulse followed by 1us+ high pulse | This is a 60-120us long low pulse followed by 1us+ high pulse | ||

| − | === Write 1 / Read from slave === | + | ==== Write 1 / Read from slave ==== |

Write of one is the same as read from slave (slave shorts the line, when it wants to signal 0). | Write of one is the same as read from slave (slave shorts the line, when it wants to signal 0). | ||

Data starts with 1-15us low pulse, after which it's the slave's turn. Whole bit lasts 60-120us, and is followed by 1us+ high pulse, like in ''Write 0'' cycle. | Data starts with 1-15us low pulse, after which it's the slave's turn. Whole bit lasts 60-120us, and is followed by 1us+ high pulse, like in ''Write 0'' cycle. | ||

| Line 31: | Line 31: | ||

| − | == Network layer == | + | === Network layer === |

| − | === Read/Write byte === | + | ==== Read/Write byte ==== |

Read or write is just eight read or write bit commands. All data is transferred LSb first. | Read or write is just eight read or write bit commands. All data is transferred LSb first. | ||

| − | === Device discovery === | + | ==== Device discovery ==== |

First lets define the term triplet. Triplet is two read bit slots followed by one write bit. | First lets define the term triplet. Triplet is two read bit slots followed by one write bit. | ||

| Line 49: | Line 49: | ||

| − | == References == | + | === References === |

Book of iButton standards: http://www.maxim-ic.com/app-notes/index.mvp/id/937 | Book of iButton standards: http://www.maxim-ic.com/app-notes/index.mvp/id/937 | ||

| − | = Bitbanging = | + | == Bitbanging == |

| − | == Motivation == | + | === Motivation === |

pit was doing 1-wire over gpio, and got me all wet about it, so I decided to take a stab at it. 1-wire is neat because you, as the name says, only need one wire plus the ground. Unfortunately peripheral MCU support for 1-wire is rare, so one either has to use a bridge (like ds2482) or use a GPIO and write some software. | pit was doing 1-wire over gpio, and got me all wet about it, so I decided to take a stab at it. 1-wire is neat because you, as the name says, only need one wire plus the ground. Unfortunately peripheral MCU support for 1-wire is rare, so one either has to use a bridge (like ds2482) or use a GPIO and write some software. | ||

| − | == Hardware == | + | === Hardware === |

While 1-wire implementations with GPIO are quite common, pretty much everybody uses separate power line. I wanted devices to use parasitic power from data line, so here's actually some trivial original work (hi, pit! :P). | While 1-wire implementations with GPIO are quite common, pretty much everybody uses separate power line. I wanted devices to use parasitic power from data line, so here's actually some trivial original work (hi, pit! :P). | ||

| Line 68: | Line 68: | ||

| − | == Software == | + | === Software === |

The GPIO uses two states. It either pulls the line low (output 0), or it releases the line (input), and the pull-up pulls the line high. Since the implementation I've learned that this pin setup is called open-drain, and is available on some microcontrollers (ie. STM32). | The GPIO uses two states. It either pulls the line low (output 0), or it releases the line (input), and the pull-up pulls the line high. Since the implementation I've learned that this pin setup is called open-drain, and is available on some microcontrollers (ie. STM32). | ||

| Line 78: | Line 78: | ||

* write 1 / read from slave | * write 1 / read from slave | ||

| − | === Reset === | + | ==== Reset ==== |

Reset is just a 480us+ low pulse, followed by 480us+ high. Not much to complicate. Pull the line low, delay, release the line. | Reset is just a 480us+ low pulse, followed by 480us+ high. Not much to complicate. Pull the line low, delay, release the line. | ||

| − | === Write 0 === | + | ==== Write 0 ==== |

Timings for write were taken from specs, to be as short as possible, with some tollerance: | Timings for write were taken from specs, to be as short as possible, with some tollerance: | ||

* write 0: pull low for 60us, release, 2us wait (total of 62us) | * write 0: pull low for 60us, release, 2us wait (total of 62us) | ||

[[File:1-wire-write0.png]] | [[File:1-wire-write0.png]] | ||

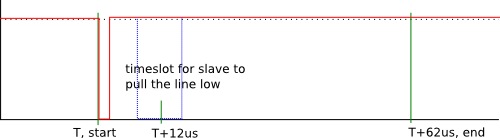

| − | === Write 1 / Read from slave === | + | ==== Write 1 / Read from slave ==== |

A write of one is also a timeslot for slave to respond. I simplified the timings into: | A write of one is also a timeslot for slave to respond. I simplified the timings into: | ||

* write 1/read: pull low for 2us, release, 10us delay, read reply from slave (if read), 50us delay (total of 62us) | * write 1/read: pull low for 2us, release, 10us delay, read reply from slave (if read), 50us delay (total of 62us) | ||

Latest revision as of 17:55, 28 February 2011

Contents

One wire overview

TL;DR

This is a short overview about 1-wire bus, so the implementation of bitbanging below will make sense.

On physical layer it's made of GND and data line (parasitic powering); It might also contain a separate power source.

The speeds reach up to 16kbps in normal mode, and 142kbps in overdrive.

1-wire is also called iButton. It's basically the same thing.

Use a pull-up of 1-5k.

Link layer

I will only mention regular speed, overdrive is similar, only timings are different.

Line is driven high by a pull-up, so master and slave basically only signal zeroes.

Reset pulse

Reset puts the device into predefined state. It's just a 480us+ low pulse followed by 480us+ high in which time devices mark their presence.

Write 0

This is a 60-120us long low pulse followed by 1us+ high pulse

Write 1 / Read from slave

Write of one is the same as read from slave (slave shorts the line, when it wants to signal 0). Data starts with 1-15us low pulse, after which it's the slave's turn. Whole bit lasts 60-120us, and is followed by 1us+ high pulse, like in Write 0 cycle.

See standard for details, under Read Time Slots.

Network layer

Read/Write byte

Read or write is just eight read or write bit commands. All data is transferred LSb first.

Device discovery

First lets define the term triplet. Triplet is two read bit slots followed by one write bit.

Device ID's are 64-bit long, composed of family id (first 8 bits), unique id for that family, and crc8 (reversed, with polynomial 0x131, last 8 bits).

For discovery master will send SEARCH ROM command and generate 64 triplets. It has to do that for every discovered device, with resets in between. In the read slots devices respond with their address bit and negated address bit. The write slot is for master to select devices which match it - the devices that don't match it will deactivate until next reset.

For responses from devices there are four possibilities:

- 0 0 - two devices answered and they have different bit on current place in address field. Master selects which device to activate/deactivate.

- 0 1 - all devices have 0 in that place in address. Master will want to write 0 here, or all devices are deactivated.

- 1 0 - all devices have 1 in that place in address. Master will want to write 1 here, or all devices are deactivated.

- 1 1 - bus error. Ie. no devices on bus.

References

Book of iButton standards: http://www.maxim-ic.com/app-notes/index.mvp/id/937

Bitbanging

Motivation

pit was doing 1-wire over gpio, and got me all wet about it, so I decided to take a stab at it. 1-wire is neat because you, as the name says, only need one wire plus the ground. Unfortunately peripheral MCU support for 1-wire is rare, so one either has to use a bridge (like ds2482) or use a GPIO and write some software.

Hardware

While 1-wire implementations with GPIO are quite common, pretty much everybody uses separate power line. I wanted devices to use parasitic power from data line, so here's actually some trivial original work (hi, pit! :P).

After some debating on the channel, we concluded a very simple scheme could work:

1k---- Vdd

|

gpio -----+---- 1-w

Of course you could still power devices via a separate line.

Software

The GPIO uses two states. It either pulls the line low (output 0), or it releases the line (input), and the pull-up pulls the line high. Since the implementation I've learned that this pin setup is called open-drain, and is available on some microcontrollers (ie. STM32).

As described in the overview, the main link layer things to implement are:

- reset pulse

- write 0

- write 1 / read from slave

Reset

Reset is just a 480us+ low pulse, followed by 480us+ high. Not much to complicate. Pull the line low, delay, release the line.

Write 0

Timings for write were taken from specs, to be as short as possible, with some tollerance:

- write 0: pull low for 60us, release, 2us wait (total of 62us)

Write 1 / Read from slave

A write of one is also a timeslot for slave to respond. I simplified the timings into:

- write 1/read: pull low for 2us, release, 10us delay, read reply from slave (if read), 50us delay (total of 62us)

This covers the lower layer, and on one above there's read/write byte and triplet. Write and read bytes are just eight write/read commands. Also, the triplet (R R W) is required for device discovery

And this is all that's needed to implement pretty much everything 1-Wire requires. The 1-wire master interface consists of (inspired by ds2482 i2c->1w bridge):

- reset

- write byte

- read byte

- triplet

Bitbang driver is located at [1]

1-wire layer in CBAOS then implements master independent device scanning and the four normal speed commands CRC calculations.

[2]

Article written by Domen Puncer <domen@cba.si>